6800 Introduction

.cr 6800 To load the 6800 cross overlay

.cr 6801 To load the 6801 cross overlay

.cr 6301 To load the 6301 cross overlay

The Motorola 6800 processor is about as old as the Intel 8080.

Over the years a few other processors were evolved from it, like the 6801, 6802 and the Hitachi 6301.

The 6802 is the same as the original 6800, only a clock oscillator and 128 bytes of RAM were added.

Some other models all have a slightly different instruction set.

All these devices are quite similar and that's why I describe all their cross overlays here on one page.

The opcode test files included in the download package show all the processor specific instructions and new addressing modes.

The 6800 can use the zero page addressing mode, which compensates generously for the limited number of internal registers that are available.

Programming Model

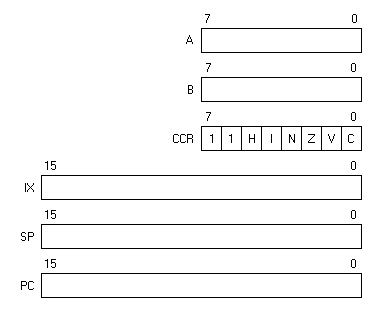

The programming model in the picture below shows the most important registers of the 6800 processor. I only include a little summary about the features of the 6800's programming model here. It is not my intention to make the original documentation obsolete, so please refer to the original documentation for further details.

Don't be alarmed by the relatively small number of registers of the 6800 compared to other processor types. The 6800 has a very powerful addressing mode called direct page addressing. This way all 256 bytes of page 0 in memory can be addressed with only 8 bits. These 256 addresses can be considered the "registers" of the 6800!

The Accumulators A and B

Both Accumulators are technically the same and can both be used for a variety of arithmetic operations.

Only a few instructions operate on only one of the Accumulators, all other Accumulator related instructions can use either of them.

Both Accumulators can be concatenated to form a 16-bit Accumulator, called D, on the 6801 and 6301 processors.

Accumulator A becomes the most significant byte of the double Accumulator.

The double Accumulator is not shown in the picture above.

The Condition Code Register

The CCR register holds all the system flags. Most flags reflect the status of the machine after mathematical instructions.

The CCR contains these 6 system flags:

| Bit 7 | 1 | Aleays reads 1 |

| Bit 6 | 1 | Aleays reads 1 |

| Bit 5 | H | Half Carry Flag |

| Bit 4 | I | Interrupt Mask Flag |

| Bit 3 | N | Negative Flag |

| Bit 2 | Z | Zero Flag |

| Bit 1 | V | Overflow Flag |

| Bit 0 | C | Carry/Borrow Flag |

IRQ interrupts are disabled when the I bit is set.

The two unused bits always read as "1".

The Index register IX

This register can be used as a 16-bit index register to point to any location in memory.

The official notation of the indexed addressing mode is offset,X, where offset is an 8-bit unsigned offset value.

Usually the offset value is $00 and that can be written in three different ways in the SB-Assembler:

LDAA $00,X

LDAA ,X

LDAA X

All three instructions have the same effect and all use an offset value of $00.

The Stack Pointer

The 6800 has a 16-bit stack pointer.

Therefore the stack can be located anywhere in RAM memory.

The stack pointer always points to the first available stack location.

A value to be pushed is stored at the location that is pointed to by SP, then SP is decremented.

The stack on a 6800 grows down in memory as more bytes are pushed onto it.

Words are pushed with their LSB first.

Subroutine calls and interrupts push the return address on the stack.

This is the address of the instruction that has to be executed when the subroutine or interrupt is completed.

Interrupts save all registers on the stack. The order in which all data is pushed is shown below:

PCL, PCH, IXL, IXH, ACCA, ACCB, CCR

It goes without saying that the pull order is just the other way around!

The Program Counter

The program counter PC is normally incremented after fetching each instruction or operand byte during program execution. The only way you can change this behaviour is with the jump, subroutine and return instructions. Also interrupts can change the program counter's value.

Timing

SB-Assembler Version 3 can show you the cycle times of each instruction when the TON list flag is switched on. The numbers presented are the number of clock pulses the processor needs to execute the instruction.

Reserved Words

The SB-Assembler 6800 cross overlay family has only one reserved word, the letter X. For the rest you may choose any label name you like.

Special Features

Indexed addressing mode

The official notation of the indexed addressing mode is offset,X, where offset is an 8-bit unsigned offset value. Usually the offset value is $00 and that can be written in three different ways in the SB-Assembler:

LDAA $00,X

LDAA ,X

LDAA X

All three instructions have the same effect, and all use an offset value of $00.

Forced direct page and extended addressing modes

One of the strongest features of the 6800 family is its direct page addressing mode. Direct page addressing mode is also called zero page addressing mode, because the 6800 can only use memory page 0 for direct addressing. With direct addressing mode you specify a memory location that can be addressed with only one byte (instead of 2 for all other memory locations). This way the 6800 can be seen as a microprocessor with 256 registers.

The SB-Assembler automatically selects direct addressing mode when that mode is available and the high byte of the address is $00 (being the zero page).

We only know for sure that the high byte of the address is $00 if there was no unresolved label in the expression identifying the address.

If a forward referenced label is used in an address expression we automatically assume the worst case situation and opt for extended addressing mode (2 bytes address field).

You may override this automatic selection of addressing mode by preceding the address field with a < or a > symbol.

The < symbol forces the assembler to use direct page addressing mode, even if the address expression contains a forward referenced label.

On the other hand the > symbol will force the assembler to use the extended addressing mode, even if the address could be resolved to a direct address.

However a Out of range error will be reported if you try to force to use the direct addressing mode where the high byte of the address isn't zero.

Examples:

0010- LABEL .EQ $10 A zero page address 8000-96 10 LDAA LABEL Appears to be zero page 8002-96 11 LDAA <FORWARD Clearly a forward referenced label 8004-97 12 STAA $12 Is a zero page address 8006-B7 00 11 STAA >$11 Force absolute addressing mode 0011- FORWARD .EQ $11 A zero page address

Overlay Initialization

Two things are set while initializing the 6800 overlay family every time it is loaded by the .CR directive.

- Big endian model is selected for 16-bit addresses and for the .DA and .DL directives. This means that words or long words are stored with their high byte first.

- The maximum program counter value is set to $FFFF.

Differences Between Other Assemblers

There are some differences between the SB-Assembler and other assemblers for the 6800 family of processors. These differences require you to adapt existing source files before they can be assembled by the SB-Assembler. This is not too difficult though, and is the (small) price you have to pay for having a very universal cross assembler.

- Not all assemblers allow you to use the shorter indexed mode.

- Not all assemblers will understand forced direct page and extended addressing modes.

- The obvious differences in notation of directives common to all SB-Assembler crosses.

- Don't forget that the SB-Assembler does not allow spaces in or between operands. Only Version 3 will allow one space after each comma separating operands in the operand field.